Home

# New RidleyWorks® Software Lifetime License

\$2,400.00

-

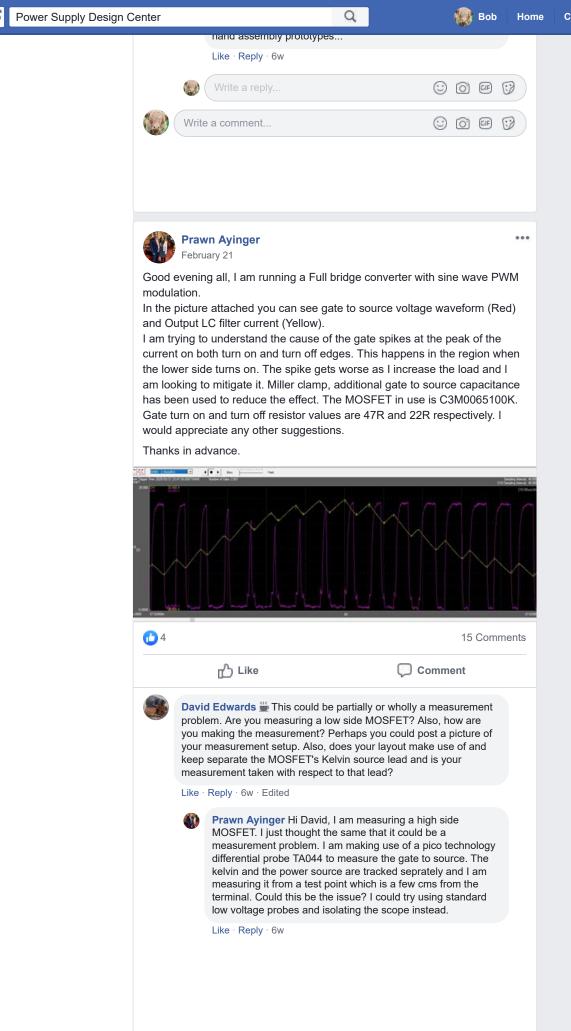

Hi everyone, I know this might be inappropriate to post here, but I think this might be the only group that actually help me.

I am a master's student in Electrical Engineering at University of Texas at Austin working in Power electronics field, under Prof.Alex, I am looking for an internship opportunity for this summer and fall 2020 in Power electronics field but not able to find any leads and my sole purpose of doing master's was to be able to switch my field from digital area (NVIDIA, where I have been doing digital work full-time) to work in the area of my interest, but I am disappointed that I am not able to do that even after working hard to get here

Marcus Lim I think Typhoon HIL is a great internship option for you. You have both power and digital electronics background and Typhoon is working on emulating real power electronics systems in the digital realm. https://www.typhoon-hil.com/careers/ You'll have to travel to Europe though.

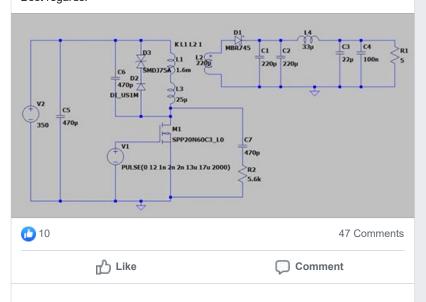

Ray Ridley © Chan is overly complex for a quantity is purely empirical. We use the following simple circuit. Why overcomplicate?

Home

Like · Reply · 4w

Stuart Wood Ray Ridley does this model also contain the leakage inductance, if you generate it from the frequency response of the primary with the secondary winding shorted?

Q

Like · Reply · 4w

Ray Ridley This model is derived directly from the Core

Put in your material, and the circuit model comes out.

The leakage is derived separately from the winding arrangement that is put into the program. We get pretty close, although we don't attempt to model the changing leakage with frequency. The world isn't ready for that yet, apparently.

Like · Reply · 4w

Stuart Wood Ray Ridley I'm sorry I'm ment the LR network for the winding loss. Does that include leakage.

Like · Reply · 4w · Edited

Ray Ridley No, separate component. We have an LR network for leakage too, but haven't activated that in our software yet.

You can see in the model below that the 10 uH leakage is not part of the winding model.

Like · Reply · 4w

Write a reply...

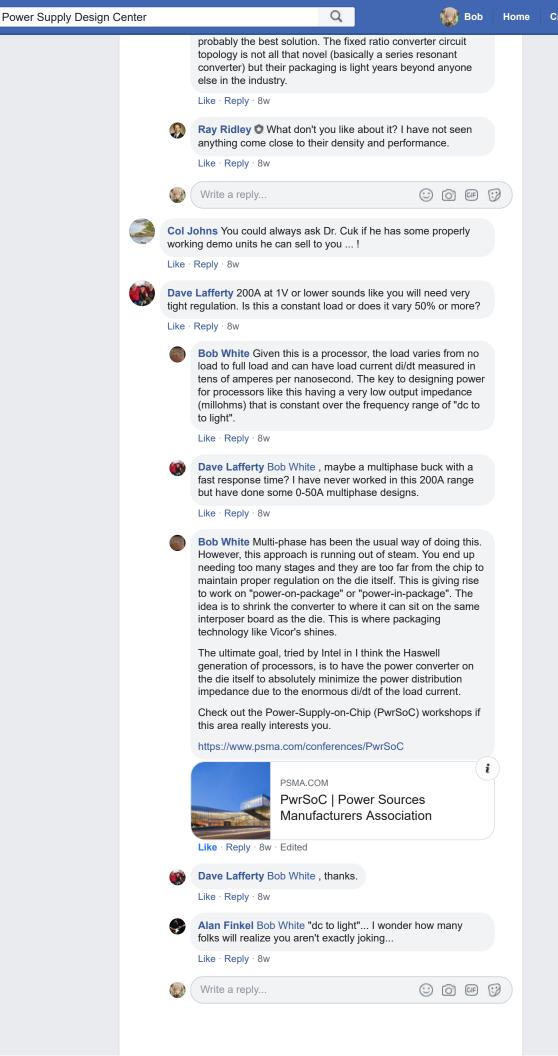

David Edwards . Hello Ray Ridley,

The Chan model captures low frequency hysteresis loss only. Your loss model is better in that it represents total core loss over frequency, but it does not model saturation, which, when needed, is a good reason to use the Chan model.

Like · Reply · 4w

Ray Ridley 1 If you have saturation, you shouldn't be designing power supplies......

Look for it, if you see it, add turns as needed, and stop trying to model it.

Magamps, self oscillating saturating topologies, flux walking?

Like · Reply · 4w

Ray Ridley The needs of the 1% shouldn't drive the model complexity of the 99%.

I know what you are saying, my first ever design depended on saturation. It was just modeled with a single line of PWL code which did fine. Later on we eliminated the need for a saturating inductor since it overheated - as do just about all of

I sincerely doubt any simulation is going to track the realities of flux walking on the bench. That's why we see a lot of examples where a transformer saturates when the designer didn't see it in the simulation.

Like · Reply · 4w

Ray Ridley Our model also captures the extra loss when you have different duty cycles.

Like · Reply · 4w

Stuart Wood I agree, but I'm trying to get a sense of what people generally do. I'm working on a white paper on modeling magnetics. I know what I do but I don't want to speak for the rest of the world.

Like · Reply · 4w

Ray Ridley Tell us what you do, Stuart Wood.

Like · Reply · 4w

Stuart Wood Ray Ridley, I've been heavily influenced by you and others. At the start of a design I don't expect simulations to give me losses. I use them for proof of concept, in the areas of large signal performance, loop stability and rough estimate of losses in my semiconductors. If thing look ok then I move to a prototype. Build my magnetics and measure them. Build my magnetics models based on the measurements. Repeat Sims to see if they reflect the higher order effects on the prototype. Rinse and repeate. I've seen companies that are trying to reduce snubber losses in sim. When they've never properly characterised there magnetics! Only have a DC resistance and an estimate for leakage...

Like · Reply · 4w

Stuart Wood My general opinion is that engineers in Areospace like to latch onto things like the Chan Model or someone's implementation of Steinmetz equation when doing worst case analysis and think they have this great model, but when they don't study these in depth. It becomes garbage in garbage out.

Like · Reply · 4w · Edited

David Edwards @ @ Stuart Wood,

Garbage-in, garbage-out is the bane of injudicious simulation.

Like · Reply · 4w

Ray Ridley Completely agree, but it is not just the aerospace industry.

Like · Reply · 4w

Ray Ridley Core manufacturer's data is often woefully inadequate. But what else can you do?

At best it is typical loss, they explicitly say that. No such thing as worst-case data.

Like · Reply · 4w

Stuart Wood Ray Ridley that's one of the reasons I think it's garbage in, garbage out.

kay kiuley 👽 vveli, not entirely. A loss estimate, even il it typical, is better than nothing. Most simulations call the core loss zero, which is even more garbage.

Q

Our models match the curves, and also move with the duty cycle of the signal. They will overestimate, if anything.

Aerospace designers are really in a tough spot. They have to do WCA to satisfy the contract. We at least help them make an informed guess at it. As long as it is backed up by good thermal data, all is OK.

Like · Reply · 4w · Edited

Nicola Rosano I use similar RL ladder models for core losses and proximity effect. Cauer or Foster syntesis network approach

Like · Reply · 4w

Ray Ridley One day, everyone will do this. Congrats, Nicola Rosano, on being one of the first in our industry to go there.

But it will be SLOOOOOW for everyone else to get there, especially as the magnetics companies are providing serious friction

With our software, it is so easy. 5 minutes in, and you have LTspice and PSIM models and circuits automatically generated, ready to run. You have to decide if it is worth spending a little money to move your analysis 100 years ahead of the conventional models.

Like · Reply · 4w · Edited

Nicola Rosano Mine. Airbus colleagues in UK confirm they continue to use that approach 😃

Like · Reply · 4w · Edited

Nicola Rosano Modeling error less than 10%. This was for 3C98 material if I'm not wrong

Like · Reply · 4w

Ray Ridley Interesting using Cs instead of Ls. I think I like that.

However the source should not be sinusoidal - has to be raised to a power or the characteristics aren't captured properly.

Like · Reply · 4w

Write a comment...

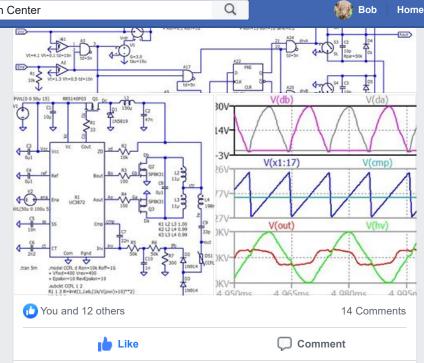

## **Ahmed Salah** March 1

Could connecting non-invasive current probes (like hall effect or rogowsky coil ) to the power circuit change the circuit performance or reduce the efficiency somehow? And why?

🚹 You and 3 others

14 Comments

Like

Jesus Elias Valdez Resendiz They will always take an small amount of energy to perform the measurment, but it can be considered neglectable in the case of active current probes

Like · Reply · 4w

Bryce Hesterman The data sheets of the Hall effect probes specify the insertion impedance as a function of frequency. The impedance increases significantly above the probe bandwidth. I expect that Rogowski probes would have less effect than Hall probes.

Ahmed Salah Bryce Hesterman ok that makes sense, thank you for the information

Like · Reply · 4w

Brian Faley If you have to lengthen the lead of power device or increase the loop inductance, the act of adding the probe can substantially alter circuit behavior for the worse.

Like · Reply · 4w

Ahmed Salah Brian Faley yes I understand. But actually even after that when I insert the probe or take it out the efficiency is different

Like · Reply · 4w

Alex Berestov Yes it could, yes it does. Why: due to the nature of things.

Like · Reply · 5w

pricing. I believe they have a lot of optional add on modules

that you probably don't need for most work.

Like · Reply · 5w

Nicola Rosano Ray Ridley I used it for years in 3 different companies. Below 15k is hard (1 network license). Without smartCTRL addon.

Like · Reply · 5w

Albert Dunford Nicola Rosano A permanent PSIM Pro standalone licnese without modules is under \$4k, there is an annual maintenance program that you can elect not to pay and then you don't get updates and low priority support. This will run any of the circuits exported from Ridleyworks. \$15K USD sounds like a network license with a bunch of modules.

Network licenses, modules for digital control, motors, code gen, links to simulink, vhdl, thermal models will add to that.

Like · Reply · 5w

Write a reply...

David Edwards ₩ Wasn't PSIM created expressly for this purpose (to measure loop gain in the transient domain)? How is this charting new territory? That the schematic is automatically generated?

Like · Reply · 5w

Ray Ridley No, it was created for speed and convergence. the sweep came later.

Like · Reply · 5w

**Nicola Rosano** I guess so. The AC sweep multisine function was created time ago and is pretty fast. I use it. The 'mapping procedure' seems to be a new feature.

Like · Reply · 5w · Edited

Hide 14 Replies

Ray Ridley You shouldn't use the multisine injection. theoretically faster if 4 seconds isn't good enough for you, but it is prone to errors.

It's a nonlinear system. You can't superimpose injections.

Like · Reply · 5w

Robert L Rauck Ray Ridley I never use multisine. The sequential sweep method is much slower for complex designs but the results are far superior. Now we are getting high speed.

Like · Reply · 5w

**Nicola Rosano** Nice point. There are two ways to get AC sweep in Psim (two different algorithms). The speed difference between them is huge. Multisine approach needs to be 'tuned' carefully to work properly.

True they are non linear system but one of psim strenght in just this: look at the stage as piecewise linear function block. I verified there is pretty good matching between AC multisine results and power stage equivalent linear model.

Like · Reply · 5w

Riccardo Tinivella Multitone analysis is the only way to get control loop from resonant topology not?

Like · Reply · 5w

Bryce Hesterman Nicola Rosano Not

Experience gained in LTspice was very useful in doing this.

Last few kinks in the fully automated setup schematic and script files are being resolved right now.

Like · Reply · 5w

David Edwards @ Ray Ridley, One of my coworkers used PSIM (I think it was PSIM). About five or so years ago I compared the transient loop-gain analysis of PSIM to SIMPLIS. SIMPLIS was faster and much cleaner, but it seems now that you have helped PSIM soup up their algorithms and programming and improve their performance.

I asked Mike Engelhardt several times to add this as a native feature to LTspice, but he didn't believe it was necessary when designing the compensation for current mode control ICs (pretty much all LTC makes). Now that Mike has left Analog Devices I don't expect LTspice to improve much except perhaps in the user interface.

Like · Reply · 5w · Edited

Albert Dunford Robert L Rauck We re-worked the sweep so that the sequential perturbation injection is much more intelligent. The original AC sweep in PSIM was very much brute force and a lot of time was wasted waiting for steady state

Like · Reply · 5w

**Albert Dunford** Riccardo Tinivella no multi-tone or msine is not the only way to get the open loop response of an LLC

Like · Reply · 5w

Ray Ridley David Edwards don't underestimate what ADI might do with LTspice. Mike was a genius at what he did, no one can ever match him.

However, he was philosophically opposed to doing Bode plots, so I wouldn't be surprised to see some improvements in that area.

ADI and LT have a culture of hiring really bright people. There are lots of PhDs from Virginia Tech and elsewhere, so I think the future is very promising.

Like · Reply · 5w

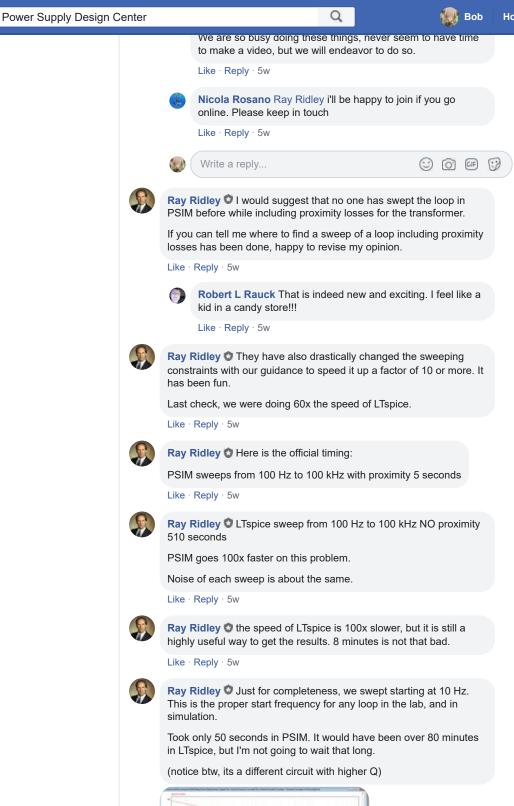

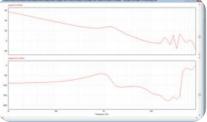

Ray Ridley ① On the PSIM algorithms - they were working way too hard at getting convergence to a given error when I starting working with them. The first attempts at the sweep function were only about 2x faster than LTspice.

We have now accelerated that to be 100x faster than LTspice which is what it should always have been capable of. A little bit of bench knowledge goes a long way in speeding up the simulation whiz kids.

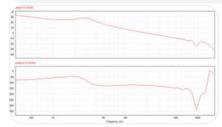

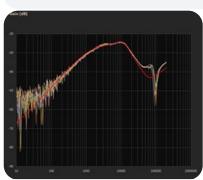

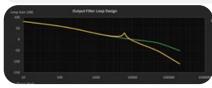

This is the latest sweep while on the phone with them just 5 minutes ago. It is amazingly clean.

Like · Reply · 5w

Nicola Rosano Is there a video about that?

Like · Reply · 5w

Ray Ridley And here is the result direct from RidleyWorks.

Like · Reply · 5w

Robert L Rauck This is a Godsend!!

Like · Reply · 5w

Nicola Rosano I made a sort of similar comparison time ago for the three basic topologies: buck, boost and buckboost (without proximity). Linear modeling vs AC sweep results were perfectly superimposed for control to output and line to output transfer functions. Some high frequency deviations were present comparing input and output impedances.

Q

I should have 'octave' files somewhere.

Anyway where possible I continue to move for Vorperian solution. With variable frequency stages Psim features (or equivalent) become necessary.

Like · Reply · 5w

**Terence Orr** What's the advantage of running a transient simulation? Is an AC sim with averaged switch model not even faster? Can you plot this on top of AC sim result to show the difference/advantage?

Like · Reply · 5w

Ray Ridley Terence Orr yes we could plot it but you can too

For well behaved systems they align well.

Like · Reply · 5w

Ray Ridley Very often you have a control scheme that has not been modeled so no small signal model exists yet.

Simple CT sense current mode with a filter on the current is one example.

Of course we do Vorperian's model as well. It takes the 5 seconds down to a fraction of a second.

Many other advantages to the small signal approach in addition. But as mentioned the models don't always exist.

Like · Reply · 5w

**Bryce Hesterman** My experience is that transient simulations of current-mode control are much more accurate than averaged simulations because the current ramp gets distorted by things like noise filter, ringing and snubbers.

Like · Reply · 5w

**Norman Elias** Have you tried the DSIM platform that they're now pushing? Al Dunford just ran a Webinar on it. I'd be interested in hearing confirmation of his claims of 2-4 orders of magnitude of speed improvement over other simulators on the market. Pretty impressive.

Like · Reply · 5w

**Albert Dunford** Norman Elias If you are in north america I am happy to set you up with a beta license so you can see for yourself.

Like · Reply · 5w

Norman Elias Thanks Albert Dunford. I'll probably take you up on this offer. Please get back to me in a couple of weeks.

Q

Like · Reply · 5w

Albert Dunford The AC sweeps in PSIM are based on signal injection. So you can determine loop gains or transfer functions of any topology or control scheme, phase shift with PCMC, LLC, 3 phase with dq control, motor drive. DCM, CCM, etc.....

Like · Reply · 5w

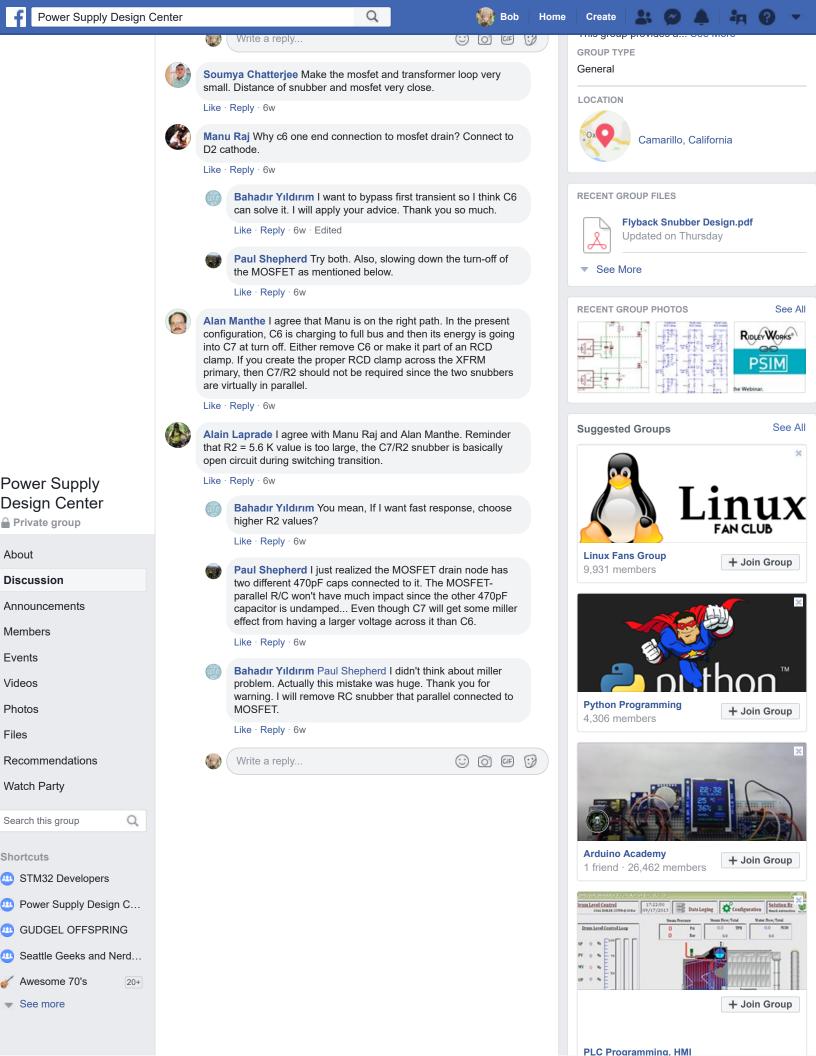

Ray Ridley Learning more about PSIM. Here is the before and after of the transfer function with and without transformer proximity

Not a huge change, just a shift in the damping of the LC filter, as might be expected.

Like · Reply · 5w

Ray Ridley Core loss made no difference to the loop. Does anyone know why?

This is another first - the transfer functions of a converter with both core loss and proximity losses taken into account.

Like · Reply · 5w

Nicola Rosano Ray Ridley intuitively speaking if you model core losses paralleling a RL ladder (high values typically) to the primary inductance, the equivalent impedance of the added branch continues to be much greater respect the primary inductance impedance one on all frequency range. It remains transparent.

Like · Reply · 5w

Colin Tuck presumably core loss is small is the main reason...

Like · Reply · 5w

Ray Ridley Not only that, there is more to the answer.

Like · Reply · 5w

Colin Tuck In the fwd topology the core loss is just a load on the HVDC - so does not participate in any type of loop filter ...?

Like · Reply · 5w

Ray Ridley that's right. It's just a parallel load on the transformer and doesn't affect the duty cycle in any way.

Hence you probably would't include it in the PSIM or LTspice sweeps since it will slow things down.

When you are doing the transient sweeps, of course, that is when it works great. Run the sim, click on the core, and you see the loss. No more tables to look up.

Like · Reply · 5w

Norman Elias Ray, do you know if the core loss display is a feature of the simulator or is it built into the transformer model.

Like · Reply · 5w

Ray Ridley We provide the simulator with our core loss model. The simulator can then provide the loss numbers to you.

We do the same for the proximity loss elements.

A Practical Approach to the Design of a Highly Efficient PSFB DC-DC...

Like · Reply · 4w

George T. Ottinger 1) Your claim about the secondary rectifiers is not correct - LLC has ZCS on secondary diodes always.

2) Your claim about always going above resonance is also not strictly true. If your input voltage and transformer turns ratio are set properly, you can operate at resonance. Resonance is (ideally) a load independent operating point. Adjust your input voltage (if possible - assuming a front end boost converter) on the fly to keep the LLC at resonance.

3) Like PSFB, the magnetizing current can be designed to give ZVS to the primary switches, but, higher Imag affects conduction losses in the switches.

Like · Reply · 4w · Edited

Manuel Escudero Rodríguez The claim of the LLC synchronous rectifiers it is correct, they are hard commutated through the primary while working above resonance (Qrr loss) even though they can be always ZVS.

Like · Reply · 4w

James Keith George T. OttingerWhat happens to the frequency during burst mode? how do you ensure the secondary side mosfets to have both ZVS and ZCS during burst mode?

Like · Reply · 4w

George T. Ottinger James Keith The LLC is just a form of a series resonant converter. The secondary side currents are sinusoidal in nature, always. Thus, your rectifiers always naturally commutate when the current "rings" to zero.

If you go above resonance, the time of secondary diode commutation is shifted from the gating of the primary FETs.

ZVS is not applicable. At the moment of switching, for ANY synchronous rectifier, whether it be an LLC or PSFB, the channel of the FET better be off and it is only the diode conducting. If the gate is still on when the diodes want to naturally commutate, you better have a good supply of spare FETs and a good soldering iron.

Perhaps you should simulate the basic circuit to see the waveforms.

Like · Reply · 4w · Edited

George T. Ottinger Manuel Escudero Rodríguez The secondary diodes only commutate when the primary side resonant inductor current equals the magnetizing current. At that point, the transformer current is zero, and the rectifiers naturally commutate at zero current on the secondary. If your synchronous FET gate is on at that time, on either FET, then you have a control problem.

Like · Reply · 4w

Manuel Escudero Rodríguez Dear George, above resonance the diodes start to COMMUTATE after the primary side devices alternate the polarity of the voltage at the input of the series resonant tank. The channel of the synchronous rectifiers can be SWITCHED on (and off) in ZVS and potentially in Zero Current. However, because they are not soft commutated (the only limitation is the series resonant inductor) there is Qrr loss. The waveforms are not sinusoidal above resonance.

Like · Reply · 4w

Manuel Escudero Rodríguez Thank you for your recommendations, I do have simulated the circuit beyond the basics, build many converters and programmed the control for them. No, I do not have any control problem.

i

gets the most usage in our common applications (3-20kW). http://www.pemuk.com/products/cwt-current-probe.aspx

We've found then accurate and reliable, with the ultra-minis being pretty robust. We have a designated one that gets used when a pair of pliers is needed to force them into odd spots and it's still going strong.

Powering them is the biggest pain in the rear. If using batteries, they do tend to eat them, and they can go a little strange sometimes when the batteries are getting flat.

My preference is to run them off the AC adapters, but that gets unwieldy if you've got 3-4 on the bench, so it helps to have some extra plug-boards mounted somewhere to keep things tidy. The bodies are also a little bit annoying, shape wise, and if you stack them then the power buttons can get pushed, leading to irritating troubleshooting. I haven't quite come up with anything convenient for that yet, but eventually may just open them and bridge the switch to be on permanently. The power LED could do with being a bit brighter, too.

PEMUK.COM

CWT Current Probe | PEM

Like · Reply · 4w

Andrew Mosqueda Before measuring, make sure that the circuit is robust because when the transistor blows, goodbye mr. Rogowski

Like · Reply · 4w

Jonathan Beaver Weird, that has not been my experience at all. We have never killed one, despite using them while testing devices to destruction.

Like · Reply · 4w

Alex Berestov Pretty damn good. It even inspired me to make my own (passive) instead of CT and calibrated it using pemuk. However it has "zeroing noise" by the looks, so if you are to measure 30A buy 30A probe.

P.S. As a student I've made Rogovski coil to control saturation in push-pull converter (What is the proper name: flux wandering??) but it really did not fly.

Like · Reply · 4w

**Brian Faley** PEM. Used the mini and ultra mini. Unless you spring for the extra shielding, they do capacitively couple high dv/dt switching edges, so there are some vertical artifacts. And they do not of course work for dc. The only complaint is that the power switch button sticks out for "on", and is in for "off". Keep spare batteries handy. We never used dc adapters, too much risk of high voltage faults. PEM has a flat rate repair price.

Like · Reply · 4w

Ray Ridley Rogowski coils are quite useful. The only problem I ran into is that the HF ringing and overshoot can be a function of the active compensation that is applied, and not representative of the real waveform.

So it depends on what you are wanting to use it for, but you might as well add it to the toolkit.

Like · Reply · 4w

Charlie Elliott As others have said, PEM. I have been using their parts for 20 years+. If you have the space for a slightly fatter coil then get one of the shielded ones. Without this you will get a bit of capacitive coupling pickup. Especially important with high dv/dts.

Like · Reply · 4w

John Baillie Charlie Elliott absolutely agree with this. Before inserting into you circuit it's interesting to place the (closed) probe close to the node you want to measure to see how much capacitive coupling there is.

Low Value, High Power, Surface...

## Q

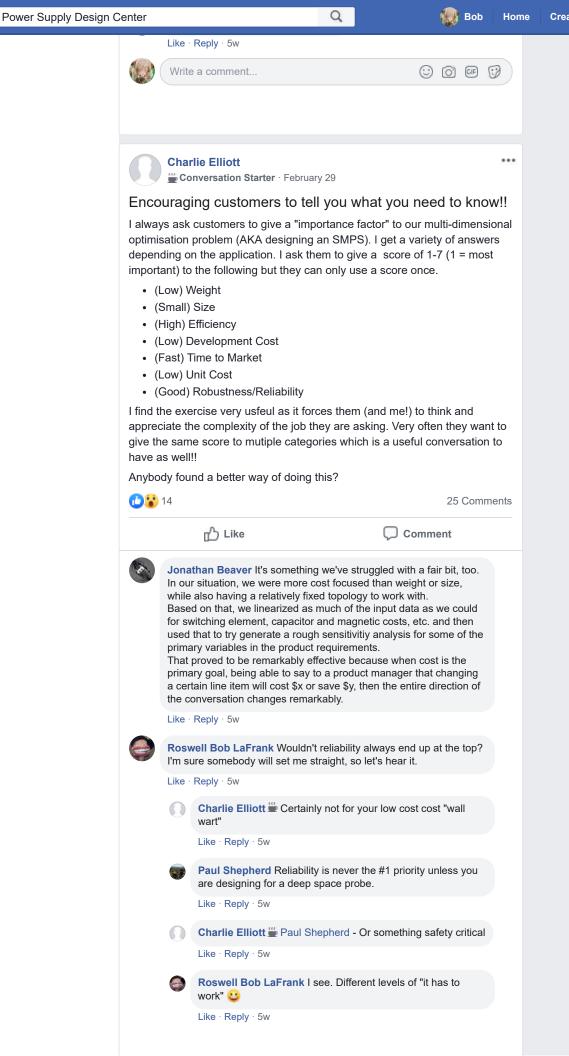

Weight most important factor - what switching frequency and core material for 20-30kW?

Following on from my optimisation scoring post, I had a new set of scores to me on Friday (1 = most important to customer)

- (Low) Weight = 1

- (Small) Size = 4

- (High) Efficiency = 3

- (Low) Development Cost = 7

- (Fast) Time to Market = 4

- (Low) Unit Cost = 6

- (Good) Robustness/Reliability = 2

Clearly to minimise weight I will want to push switching frequency up and I have the option of using expensive core materials. My gut feel is to look at Nanocrystalline/Amorphous for the transformer(s). Anybody disagree?

Charlie Elliott Jonathan Beaver - Out of interest can you say what type of cores you were using? Did you pot them and if so with what?

Like · Reply · 5w

Like · Reply · 5w · Edited

**Jonathan Beaver** Charlie Elliott MK Magnetics I-bars to create a large custom shape.

We gave up and changed tack to several smaller units. Edit: Smaller ferrites on standard core shapes, rather than something large, expensive and unwieldy.

Our thermal requirements made the cooling of it unlikely, even with liquid cooling directly in contact with the magnetic elements.

Like · Reply · 5w · Edited

Col Johns For 30kW you either make 10 modules @ 3kW at 200kHz (for min size) or skip to 35kHz for the whole thing ...

Like · Reply · 5w

Charlie Elliott 3 x interleaved 10kW blocks at closer to 100kHz with ferrite?

Like · Reply · 5w

Col Johns you can do 10kW at 100kHz ( a lot of forklift chargers do 6kW at 100kHz ) but it can get messy ...

Like · Reply · 5w

**Daniel Pruna** High sw freq. and high power are fully compatible. https://www.iisb.fraunhofer.de/.../200\_kw\_full\_sic\_dcdc...

IISB.FRAUNHOFER.DE

200 kW Full-SiC DC/DC Converter

i

tnese rantastically dense prototype systems. The engineering is plentiful and superb. They often make use of bleeding edge technology to get there. Not sure how realisable it is for a product though?

Seeing that sea of large MLCCs makes me skeptical that it will last very long on the vibration table unless there is some serious mechnical structure and AV mounts employed =

Like · Reply · 5w

Col Johns This sort of thing is great as a spur to new designs and no doubt Fraunhofer is in direct competition with ETH Zurich - so they have to come up with something "good" now and again - but if it is fixed step down then it is a limited "break thru " (from 2014) a real DC/DC needs to be able to operate at near no load and with a fairly wide Vout range - this is why LLC ( CLL ) cannot be used in many apps as it cannot go to 0V Vout ... similarly for PSFB full current at low Vout is a no-no for many designs ...

Like · Reply · 5w

Stephen Berry Col Johns I have designed PSFB converters to drive superconducting magnets. With care they can run all day at full current (8000A in my case) into a perfect short.

Like · Reply · 4w

Col Johns Ah yes - but designed for it, we did an MRI design for 2 quadrant 12V 600A 50ppm way back - using simple H bridge - the main load is the Cu leads to the magnet ...

Like · Reply · 4w

Atish Tailor Stephen Berry for your Interest that particular PSU is still considered successful and still in production. We are now working on a 500A skinnyer version..

Like · Reply · 4w

Write a reply...

Arief Noor Rahman What about the weight for your cooling system?

I made 20kW PFC...around half of the weight is for heatsink+fan

Like · Reply · 5w

Arief Noor Rahman w My PFC just operate at 12kHz Fsw because we use igbt

Like · Reply · 5w

Charlie Elliott Indeed cooling system weight (including any potting compound used) can add a lot on.

Like · Reply · 5w

Alex Berestov My gut feeling is to use soft switching as main volume/weight reduction factor.

Losses are on par with a ferrite, however you can double flux density. This may be beneficial in DC/PFC inductors.

Now bad news

It's hard to get more than 0.5....0.7T from nano at 50...100k. Keep in mind that alloy density is about the same as Fe i.e. 7.8 almost two times of a ferrite. There could be no real incentive weight wise

Cooling is also impeded in tape cores. .

Unless you going to use toroidal X-formers stay away from nanocrystal/amorph even good ones with cobalt Fringe field and shorts at the cut increase losses 5 to 10 times. Cheers

P.S. Nnocrystal/amorph technology should of been more mature (less expensive) after 40 years.

Like · Reply · 5w · Edited

Home

uensity (0.75 1- 1.5 1) showithor the FTG toroids ( powe iron, amorphous Kool mu, Xflux etc) by Magnetics Inc are not practically usable at such high flux densities? Meaning can't I use the kool mu at 0.5 T ( datasheet shows 0.75 T). Although no information of temperature is given. But, seems like the calculations shown by Magnetics Inc for PFC boost show that Bmax of around: 0.5 T is reached. https://www.maginc.com/.../Kool-Mu-Cores/PFC-Boost-Design

Like · Reply · 5w

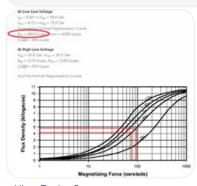

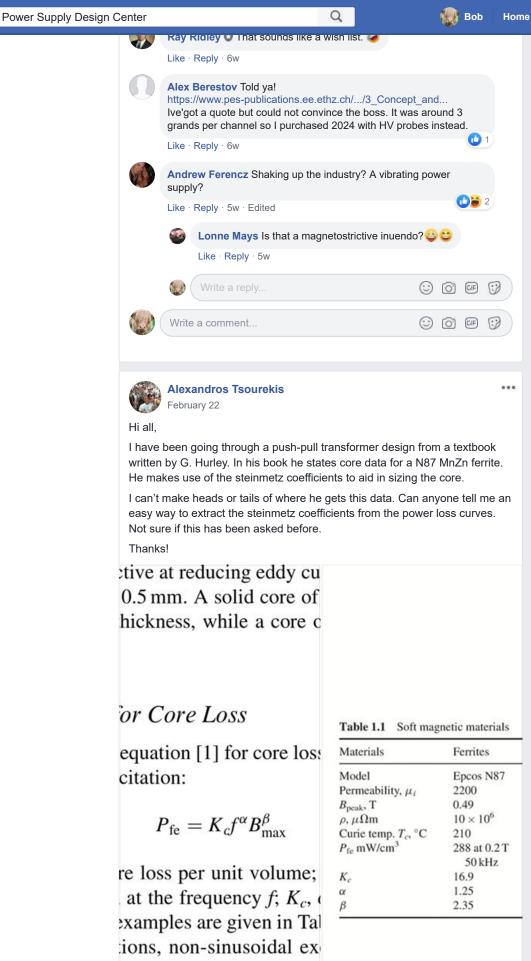

#### Venkat Karthik

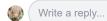

| 1 | Material  | Alley<br>Companion | Care Sans | Kin    | Relative<br>Cost | Setteration Flax<br>Density (Seale) | Carle<br>Imperators | Comparation<br>Suspension | , Serie. |

|---|-----------|--------------------|-----------|--------|------------------|-------------------------------------|---------------------|---------------------------|----------|

| ľ | Andles    | 1453               | fee       | Setter | Refer            | 1.5                                 | MF.C.               | -37°C to 133°C            | 180      |

|   | Apt for   | 5/8                | Relates   | 54     | Adm.             | 15                                  | 5801                | entwarr.                  | 199      |

|   | Sail Sy   | 1458               | law       | Sed    | liw              | - 13                                | 500"1               | -01°Ch/30°C               | 100.600  |

|   | 87        | 1486               | Series .  | Sele   | 100              | 875                                 | 401                 | 611043810                 | 3.00     |

|   | Ret       | 8/9                | N/A       | Bet    | lav              | 14                                  | 7001                | 67(6)001(                 | Stiller  |

|   | Set Packs |                    | fighet    | And    | (ped             | 13:15                               | mr.c.               | -BPC67PC                  | 500 Mb   |

|   | Jank      | Special            | Level     | fee    | lined            | 8.46                                | 10-501              | bolk                      | - Badle  |

Like · Reply · 5w

Alex Berestov Here is a quote from metglas/hitachi it was referred to:

Like · Reply · 5w

Alex Berestov And yes I did use such materials both cut and uncut, pun intended, since late 80's.

From the pic above FT3 material in container (Permalloy anybody) easily operates at B of 0.5...0.7 @ 50...100kHz. Real material is better BTW. However impregnated is not as good cut core even worse.

P.S. Managed to find old spreadsheet for inductors, PFC inductor, 3.3kVA/phase 50kHz, F3CC0040. H=6680, B=.76, H~=930, B~=0.105, Pcore sin=8.2W, Im=27A, Pcu25=4.6W. In reality, under forced air worked @ 7kW.

Like · Reply · 5w

Write a reply...

Arief Noor Rahman # I cant really say about magnetic material...

another way to make reduce converter weight is by paralleling many switches to reduce the total losses and distribute it over larger surface...reducing cooling requirement...

Modest Fsw at 20~30kHz should be good enough Two phase interleave may help as well

Like · Reply · 5w

**Hamish Laird** If you truly need robustness as a 2 then take really good care of the nanocrystaline core as they have some fantastically weird failure mechanisms from shock and vibration.

Like · Reply · 5w

Colin Tuck In that lineup, assigning reliability (quality) = 2 is a little at odds with unit cost = 6 and dev cost = 7 lowest weight (=1) strongly implies a lowish size which usually requires significant engineering input and testing ...

Like · Reply · 5w · Edited

Charlie Elliott Colin Tuck I should have been clearer. The scores are for Low unit and development cost! The customer is telling me we can put in plenty of engineering and use more expensive parts as those scores have lower priority.

Like · Reply · 5w

**Tony Salsich** Nanocrystalline cores are at their very best as CM chokes. Yes, they are somewhat delicate, but the boxed cores are fairly well protected. In fact high mu (10-15k) Ferrite is also easy to damage with shock. For either type of material the mu drops if stressed.

Like · Reply · 5w · Edited

Alex Berestov Most failures we had were from improper handling, mostly from mechanical stress, magnetization curve becomes like 100 times wider along with huge magnetostriction. Beware of the rust - most amorphs do.

Like · Reply · 5w

Charlie Elliott # I had unexplained significant increase in core loss on a prototype using some VAC cores a number of years ago (20!). I had always wondered whether they had been stressed somehow to cause the problem. They were potted in a reasonably hard material for good thermal conductivity and I was assured there was no magnetostriction to worry about but ....

Like · Reply · 5w

**Alex Berestov** Magnetostriction was a result of damage. Plastic container became deformed during transformer impregnation process: overheated.

Like · Reply · 5w

Charlie Elliott Meanwhile on the flip side of mechanical stress increasing core loss, let me share a little story. When I worked for a division of Emerson Electric involved in motor design, I visited a factory in the USA. Of the many different process areas I saw, the one that intrugued me most (intellectually) was the "Watt knocking". This involved some guys with arms like tree trunks picking up piles of stamped motor laminations and throwing them down on a large metal table to "knock the watts out" prior to the lams going into the annealing oven. The official line (from the engineers) was that this was to stop the lams sticking together so they were properly annealed and coated. The folk lore of the guys working on the line was that there was something else going on and you had to knock them just the right amount to let the watts out!!

Like · Reply · 5w · Edited

Charlie Elliott "I have edited the scoring metrics to be clearer.

Like · Reply · 5w

Alex Berestov If you apply vibration to an iron piece in a presence of Earth magnetic field for prolonged amount of time - it gets magnetized in a direction of the former for the fact. Stamping does exactly that. Perhaps mechanical shock was a cheap "degaussing".

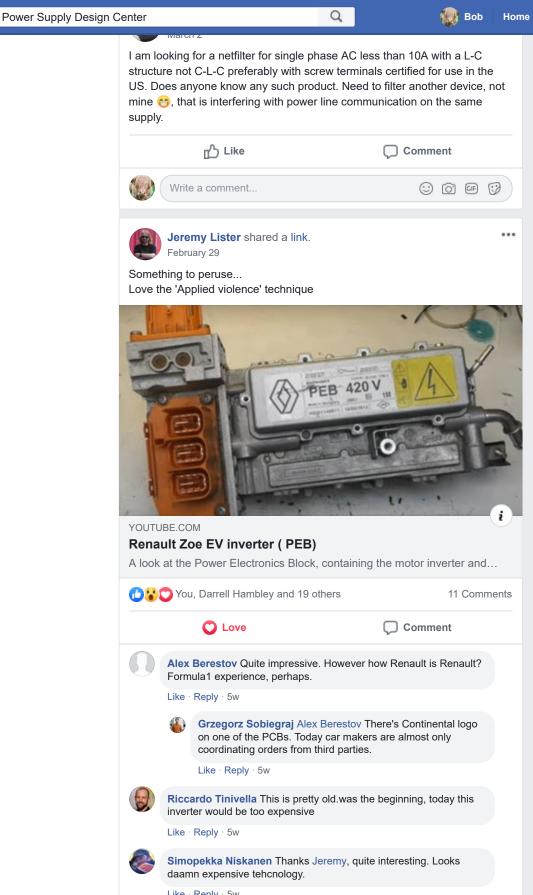

Like · Reply · 5w Jonathan Beaver Very interesting, looks pretty typical for early EV electronics from what I've seen. Huge, expensive and complicated, but probably fine for something getting made in the 10-100k/a range. I replaced the on-board charger in my older Nissan Leaf and it's

remarkable just how large and heavy that unit is for a 3.3kW on-

board charger. Like · Reply · 5w

Home

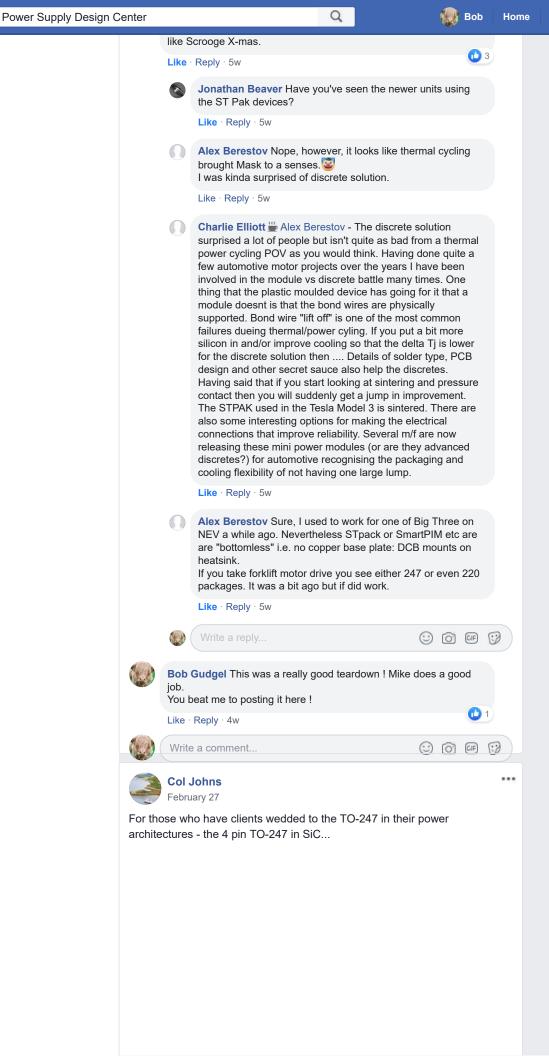

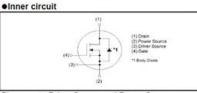

| $V_{DSS}$                  | 1200V |

|----------------------------|-------|

| R <sub>DS(on)</sub> (Typ.) | 40mΩ  |

| I <sub>D</sub> *1          | 55A   |

| Pn                         | 262W  |

### Features

- 1) Low on-resistance

- 2) Fast switching speed

- 3) Fast reverse recovery

- 4) Easy to parallel

- 5) Simple to drive

- 6) Pb-free lead plating; RoHS compliant

Please note Driver Source and Power Source are not exchangeable. Their exchange might lead to malfunction.

🚹 💟 You, Jay Philippbar and 10 others

32 Comments

Like

Comment

Col Johns We have used the previous std version with +15V on and -3V off - still going in the field ...

Like · Reply · 5w

Jonathan Beaver We've found the high internal gate impedance (7 ohms in this device) to make life somewhat difficult with this generation of ROHM FETs but otherwise, the 4 leg package has proven to work out well with a variety of other parts.

Like · Reply · 5w · Edited

Col Johns Agreed, even the SCT2080KE has 6.3 ohms, ACR @ 1MHz

Like · Reply · 5w

Jonathan Beaver Col Johns Yeah, we've harassed them about it a bunch and were assured that they're aware of the issue and it'll be better in the next generation.

Like · Reply · 5w

Col Johns Jonathan Beaver do you chaps have a website ..

Like · Reply · 5w

Jonathan Beaver Col Johns No, sorry. It's on the 'to do' list! We're a 2-man band who used to work with Qualcomm's wireless EV charging tech, now out on our own.

Like · Reply · 5w

Write a reply...

Cameron Stewart Gate impedance 7 ohms?(!)

Like · Reply · 5w

Col Johns Yup 18Vpk at turn on gives ~ 2.6A into the gate ... 40nS to 17V on the gate ... with inductive drive ...

Like · Reply · 5w · Edited

Jonathan Beaver Or, worryingly, with -3V drive, Vgs(th)min adjusted for 150C junction at 1.7V, that's only 670mA to turn on parasitically, worst case.

We popped a few of the 80mR versions. Fun times.

Like · Reply · 5w · Edited

Col Johns luckily resonant gate drive gives plenty of oomph to get to -3V and stay there ... we only run to 115degC junc

Like · Reply · 5w · Edited

inductance. That's a long round trip distance.

Like · Reply · 5w

David Edwards . Hello Brian Faley,

At least for MOSFETs a few tens of nano-henrys in the gate drive circuit don't mean much, but any source impedance common to the DS circuit and the GS circuit is to avoided if possible. I imagine that the source leads in the four pin TO-247 package each have their own bond wires directly to the source pads.

Like · Reply · 5w · Edited

paralleled TO-Leadless 300A devices. The gate drive was unipolar for cost reasons. No way that could ever have been done with D2pak-7 lead, TO-247 would have been laughable. TO-247 is about five times higher source inductance. During fault conditions, all the resonant transitions softening the blow of normal operation are out the window. I have been telling mosfet vendors for decades to get the leads out of their packaging and start treating them like the rf devices they are. Few listened, even though we were one of the largest customers for 60V mosfets on the West Coast. Kelvin leads are a start, but it's not a very high hard switched frequency even on a 4 lead package before things blow up without negative drive. I can see exactly why Alex Lidow of EPC has been preaching chip scale packages. It's time to join the 21 st century. TO-247 deserves to be buried. It's decades older than me, and I've been doing this for 38 yrs.

Like · Reply · 5w · Edited

Stephen Berry Charlie Elliott I was in a division of Emerson Electric in the early '90's. We used early HEXFETS from IR. We designed a 10kVA UPS running at 20kHz. Quite twitchy to get it working and we had to buy new scopes and probes to see the edges. Production started, but they started failing in the field. On investigation, IR had changed the internal gate resistors. We found it by connecting gate and source with drain and source on a DC PSU. A nearby coil was connected to a signal generator. The FET blew up when the frequency got to 100MHz.

Like · Reply · 4w

Write a reply...

Andrew Ferencz But you have to figure 1200V, 0.04 ohms, ... even with 7 ohms of internal resistance - it is amazing. A three-leaded device can cause a lot of extra ringing and noise from the common source inductance. So you can't use this at 50MHz .. but I bet if you compare the gate charge/resistance of this part with a MOSFET you are either close to the same or better. And frankly do you really want to hard switch a 1200V node at 1nS? 50A, 1nS ... no way no how will that will ever happen with a leaded package. 1nH = 50V ... What would be needed to know how to make it work reliably in a half bridge - how much external R for turn on is needed to prevent cross conduction - or how much negative drive?

Like · Reply · 5w

Jonathan Beaver In our application (PSFB with variable loading), it simply doesn't have enough margin against parasitic turn-on under high dV/dt conditions. Max dV/dt is around 25kV/us which is pretty slow for SiC. By comparison, we replaced it with a USCi part which we were pushing towards 80kV/us, measured.

Like · Reply · 5w

Andrew Ferencz Jonathan Beaver Thanks for that. I know in the high voltage GAN world (which I think isn't ready for prime time) Panasonic came out with a part that was ... lacking. I have been looking at USCi parts for inverters. Any advice from experience is worth a lot.

Like · Reply · 5w

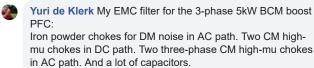

Ray Ridley Vuri de Klerk nice how is the efficiency for tha bcm?

Q

Like · Reply · 5w

Yuri de Klerk I never had a load for 750Vdc, so only tested in combination with the next stage: Two fet forward with synchronous rectifiers: 24V/200A. Total efficiency 90.5%. The PFC chokes stay much cooler than I could have guessed. Next design I think can do with 3x E42/20 for this power.

Like · Reply · 5w

Colin Tuck Would love to see the input current waveforms if some are available ...

Like · Reply · 5w

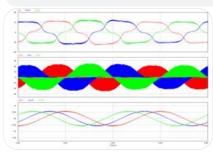

Yuri de Klerk I have no pictures of real measured current. It looks a lot like the simulation.

Like · Reply · 5w

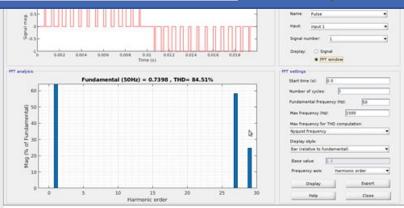

Yuri de Klerk Harmonics analyzer was used to stay below the limits in the standard. I had some trouble with 13 15 19 harmonic but was solved with tuning of the harmonic injection.

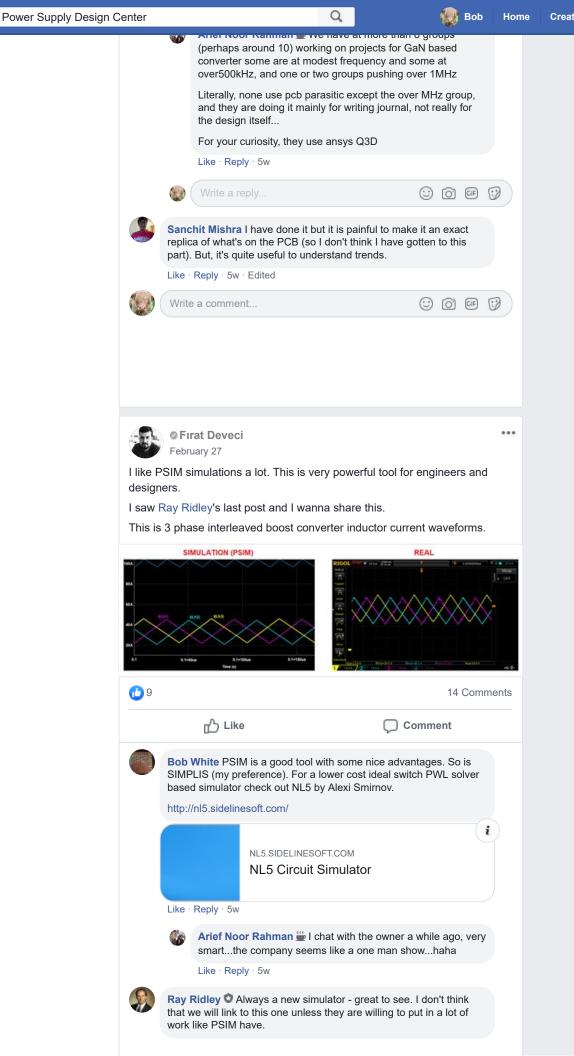

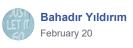

| Harmonic order | Maximum permissible<br>harmonic current |  |  |

|----------------|-----------------------------------------|--|--|

|                | A                                       |  |  |

| Odd t          | armonics                                |  |  |

| 3              | 2,30                                    |  |  |

| 5              | 2,30<br>1,54                            |  |  |

| 7              | 0,77                                    |  |  |

|                | 0.40                                    |  |  |

| 11             | 0,33                                    |  |  |

| 13             | 0,21                                    |  |  |

| 15 ≤ n ≤ 39    | 0,15 💆                                  |  |  |

| Even !         | harmonics                               |  |  |

| 2              | 1,08                                    |  |  |

| 4              | 0.43                                    |  |  |

| 6              | 0,30                                    |  |  |

| 8 s n s 40     | 0.23 8                                  |  |  |

Like · Reply · 5w · Edited

⊕ @ @ @

Rogério Junior Dr. Ray Ridley, what do you think about creating a similar topic for transformers? I have some interesting photos to share about high frequency transformers for SST applications.

Like · Reply · 5w

Charlie Elliott Progério Junior - Please do create that post -I would be interested and I am sure many others would be as well.

Ray Ridley It's a good excercise, thanks for doing this Charlie

Elliott.

Like · Reply · 5w

Like · Reply · 5w

Charlie Elliott

"Premium server PSU" score?

(Low) Weight - 7

(Small) Size - 3

(High) Efficiency - 2

(Low) Development Cost - 5

(Fast) Time to Market - 6

(Low) Unit Cost - 4

(Good) Robustness/Reliability - 1

Home

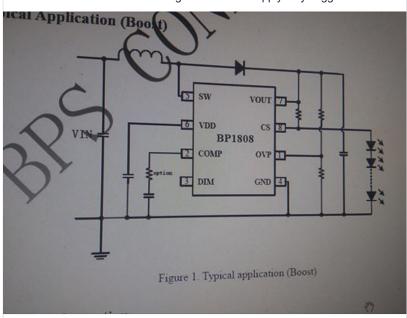

Hello friends.

I have design 3W boost converter using ic BP1808.

Vin- 12V

Vout- 36V, 100mA

Working fine .

But when i comes to emission test there is failure in RE and CE Which is at 450 KHz 78 uV db..

I don't know about EMI filter design for dc to dc supply..any suggestions.

Q

C 3 29 Comments

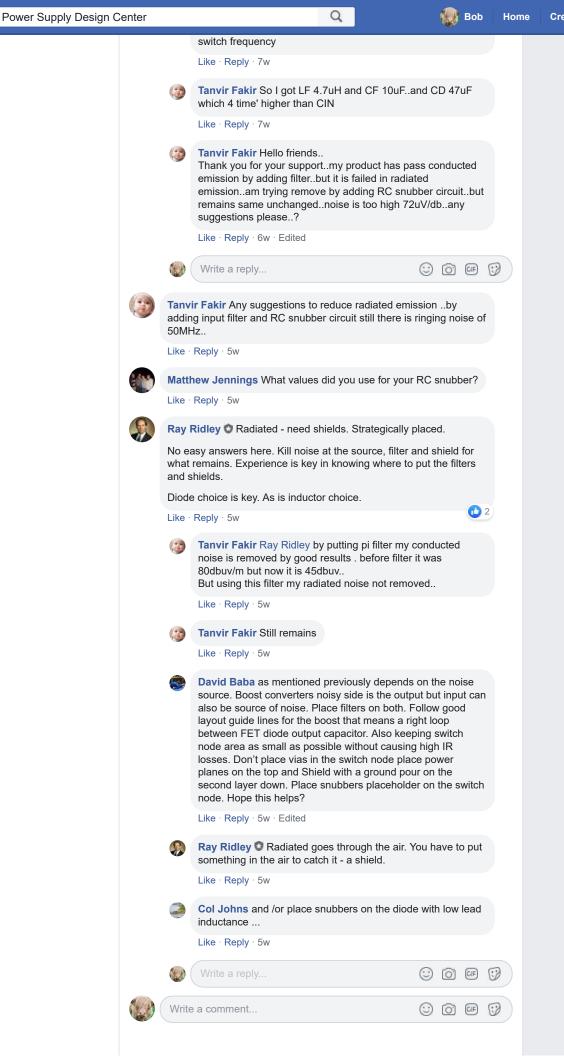

Alain Laprade Datasheet states this is a 420 kHz device. You are wrestling with the fundamental harmonic getting back to VIN. You need to add an input EMI filter. If you don't want to do the math yourself for the filter design, I recommend going to the IC manufacturer's web site for a demo board example to see what they recommend as a starting point.

Like · Reply · 8w

Shiv Kumar Mishra I would suggest review your layout as per design recomendation in datasheet. Try reducing ground loop area. Most of CE and RE problems can be overcome by reducing gnd loop. Could you tell us at what frequency your buck converter operating. You may need some input filter of targeted frequency.

Like · Reply · 8w

**Tanvir Fakir** Shiv Kumar Mishra thanks ..it is booat converter..and operating at 420KHz Freq

Alain Laprade Example given by Shiv above is incomplete. It needs an input filter.

Q

Like · Reply · 8w

Shiv Kumar Mishra I just downloaded one imgae from web and uploaded to have intial review of.

Like · Reply · 8w

Frank Warnes Measure the switching waveform on pin 5. If there is a lot of ringing a simple RC snubber might help. Also make sure your inductor is the right way round. The switching end needs to be the start of the winding so that the input end shields the noise from getting out. This should sort out the common mode noise

Like · Reply · 8w · Edited

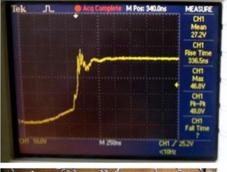

Tanvir Fakir Frank Warnes see the waveform across pin 5..i dont think it is so large noise

Like · Reply · 7w

Tanvir Fakir Frank Warnes hi frand i added rc snubber circuit across pin 5 and ground..but still ringing noise is there

Like · Reply · 7w

Tanvir Fakir I have added rc snubber circuit but still there is ringing noise

Like · Reply · 7w

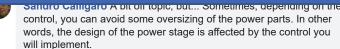

Ray Ridley Please, make a little effort to turn your graphics the right way!

Like · Reply · 7w

Tanvir Fakir But I don't think ringing noise will affect on conducted emission test

Like · Reply · 7w

Tanvir Fakir Rakesh Panda still finding solutions for CE..any suggestions?

Like · Reply · 7w · Edited

Here is a random thought. If you listen to the semiconductor companies, you would think that the control chip is the heart of a power supply, the most important component.

I am very much a controls person, but I don't think of it that way. The hard work and largest parts are elsewhere, in the magnetics, layout, power devices, thermal, etc. These all get designed first. The last step in the paper design is picking a control chip to fit the job, but the main power design is already done at that stage.

Many control chips, digital, analog, sophisticated or simple can often do the same job. That's why we see a huge array of different parts from one design review to another.

🚹 You, Jay Philippbar and 61 others

54 Comments

Comment

Colorado Mike Doherty Be careful tying the future of a product to a single-source component.

Like · Reply · 6w

Cameron Stewart There are too many control chips to choose from.

This is just in the mixed signal realm, without talking about DSP control, programmable logic array design, or the bevey of other "technology du jour" offerings to choose from.

I would politely describe the control chip situation as "chaotic and overwhelming".

Then there is the learning curve you are privileged to experience, discovering the undocumented bugs in the new control chip you were adventurous enough to try out.

If you are unhappy with the control chip you are using, by all means find another. But if the chip selection you have been using still works for you, I see no need to go looking for something new, just for the sake of it being new.

Like · Reply · 6w · Edited

Alex Borisevich controls chips are prone to silicon bugs. and smarter the chip, more severe silicon bug can be. and thus you stuck with a thing that you cant change. power electronics and magnetics you can redesign and tune. but the controller you can just drop and try another one

I'm thinking about digital control and simple converters (like an inverter) doing tough tasks.

Like · Reply · 6w · Edited

Yuval Iz I never use new control chip's in my design,

Always read chip errata and for most chip I wait a year or two before I design with them.

Using this method I minimize silicon error to minimum

Like · Reply · 6w

Broox Le Well, if it's a sufficiently complex controller, sometimes even a few years in, it still has bugs/caveats which are not publicly documented or well-known - partly because few people fully check their designs under all the myriad of conditions and happened to catch it on the scope, and then some IC manufacturers who do have customer forums where they claim they want users to ask questions & share knowledge, actually DELETE polite cordial posts that describe real undocumented issues!

Like · Reply · 6w

Kevin Azul

Like · Reply · 6w

Charlie Elliott I have two things I constantly tell my junior engineers:

- 1) The more complex something is, the more there is to go wrong. This applies to designs in general and ICs in particular. The heavily integrated parts with loads of functions and very few pins can be challenging.

- 2) The wider you open the window, the more the sh\*t flies in!! Don't make the bandwidth of anything wider than it needs to be. An increasing challenge as your switching frequency goes up.

Like · Reply · 6w · Edited

Graham Ward I agree. The actual power side of things (accommodating thermal design, component efficiency and density, parasitics, good gate drive etc.) is the most costly bit. Get any of that wrong and you incur significant cost and effort to rectify the problem. While the control side is no less complicated, an oversight is usually easily rectified by changing a resistor value in your feedback loop for example, or changing a parameter or property of your digital control loop.

Like · Reply · 6w

David Seal I have long started each design I make by stating out loud the KISS engineering principle: "Keep It Simple, Stupid." The I.C shown, if used to run or control a power supply, would be the equivalent of using a sledgehammer to kill a mosquito: it can be done, but oh the effort involved.

Like · Reply · 6w

Ray Ridley There are so many controllers out there at this point, there are not enough engineers to get to the bottom of how they all work and what their latent flaws might be.

There are at least half a dozen I really want to try ourselves, but there just isn't time to get it done.

requirements from the application perspective. Power electronics is going in more and more high power applications EV , solar etc that indeed require a lot of the complexity to function and deliver benefit. There are myriads of communication protocols to deal with , safety and security hedges and control flexibilities to achieve ZVS, hysteresis control etc.

Q

Like · Reply · 6w

Darrell Hambley I totally agree with Ray's OP: "magnetics, layout, power devices, thermal, ..all get designed first. The last step in the paper design is picking a control chip (or chips, plural). My fellow Mech'l engineer and I are currently designing a complex high power system. As we've done before, all my work is designing magnetics, calculating power loss etc as we manage heat flow and play Tetris to fit it all in the enclosure. I have no worry about finding an IC which has a ramp compared to a feedback signal.

Like · Reply · 6w

David Edwards # High power complicated topologies such as inverters and induction motor control generally have lowish switching frequencies. For these, there is no dedicated quasi-analog controller (except for housekeeping) as the main control most likely will be an all digital micro-controller.

Like · Reply · 6w

Darrell Hambley ...or, all discrete analog control.

Like · Reply · 6w

Ray Ridley So at the end of the power design, you choose the all-digital controller which makes sens in many cases. Then you have the myriad of choices of which of the many options is the best for your application.

But, again, the actual choice of the chip comes last and doesn't determine the power converter choices.

Like · Reply · 6w

David Edwards . Hello Ray Ridley,

What I wish really would come last is the design of the enclosure. The initial layout should be without constraints and for maximum performance to prove the basic electrical design. Package size and mechanical design should be last.

Like · Reply · 6w

Ray Ridley Constraint #1: Price

Like · Reply · 6w

Ray Ridley O Constraint #2: Box

Constraint #3: Schedule

Constraint #4: Development price

Fortunately, in our company, we have the option of saying "no" to many design jobs since the needs just can't be met.

Like · Reply · 6w

Charlie Elliott # Ray Ridley I very often ask customers how they would like to prioritise your #1-4 plus a few others by scoring importance of each one. Can you guess how most reply 🎑 👺

Like · Reply · 5w

Col Johns Charlie Elliott , Price, Quality, Speed of delivery pick any two and the third is a function of those picked ...

Like · Reply · 5w

Write a reply...

manufacturers are better some not so. Most of the times you do not have pin to pin substitute.

However NS, Unitrode, Motorola used to have kind of "school of design" a la "school of thought" yielding well thought out IC's tailored to PSU designer's needs.

Like · Reply · 6w

Seppo Turunen Why not use a small FPGA? I am currently using a Lattice XO2-2000 and a couple of A/D converters to control a 1kW current-fed half bridge resonance converter prototype. The control functionality is fully contained in a technology independent VHDL design file so that there is no need to decipher controller data sheets or to guess how microcontroller peripherals are supposed to work.

Like · Reply · 5w

**Col Johns** Why not...? how many engineer hours has it taken you to get "near working"? how many more hours for a solidly engineered product ...?

Like · Reply · 5w

Seppo Turunen Col Johns I suppose what is relevant here is to compare the two approaches and, if I understand right, you want to point out that FPGA design is a real work item that requires justification. I could not agree more. If a commercial chip does the job, there is probably no point in replicating its functionality with an FPGA. However, if the required topology, timing, sequencing, security or feedback control is not supported by the controller, it may, in my opinion, be a faster and more predictable choice to program an FPGA to do exactly what is needed rather than to twist the commercial chip by building a kludge around it from discrete components. Also, as an alternative to an MCU, an FPGA could provide faster and more deterministic control. I am clocking the FPGA with 50 MHz so that I have a 20 ns cycle accurate control over everything. In contrast with SW design, VHDL design is parallel, so that adding functionality does not slow down anything designed earlier. In terms of logic design, we are talking about a fairly small project. Mine currently has eight pages of VHDL code and it includes, in addition to the SMPS control, a few auxiliary functions such as LCD control.

Like · Reply · 5w

David Edwards # I am not an FPGA expert, but in the past, FPGAs were expensive, large (way too many internal gates and lots of pins) and required multiple power supplies. Are there now inexpensive, 3.3 volt single supply FPGAs of modest internal size and external pins (<=48)?

FPGAs have the advantage that they can be reconfigured every time they boot up so that field updates are easy and their function can be altered by the main micro-controller depending on user input. I see one of their biggest advantages is speed, which allows creating digital ramps with extremely high precision for precise timing and PWM. These can be created using multiple pipelined ripple counters where each added pipelined stage only cost one clock cycle delay.

Because FPGAs don't do analog well, one has to think outside the analog box to create all digital control mechanisms.

Like · Reply · 5w

**Chris Merren** I have used the Xilinx zynq 7000 series SoC with SMPS with good results....

nas no second source? I wonder what the typical production lifetime is of such a part?

Putting a small FPGA on the same silicon or at least the same header as the micro-controller could be very attractive for power product use. Many micro-controllers have PWM modules, which are set up with registers rather than code, so they steal very few cycles from the main processor and processes.

Micro-controllers with three PWM phases are common, but what if you want to have eight, sixteen or some other number of phase outputs all equally spaced in phase over 360 degrees? Programmable (connection configurable) hardware logic would be very good for that.

Like · Reply · 5w

Chris Merren David Edwards The big issue with many microcontrollers is the A-to-D are total BS.... Sampling rate is poor and the data sheet is fool of fibs....If you use too many resources the sampling rate drops... The FPGA is the way to go, especially in the A-D dept and the latency issues with control loops...

Like · Reply · 5w

David Edwards Do FPGA analog-to-digital converters have good over-under voltage protection and are they available on small FPGAs? Also, some of the specifications for some of the FPGA analog comparators I have seen have not been impressive.

Would any members of this group care to recommend a small FPGA suitable for power conversion products? (Should be single supply, perhaps with A/D converters and analog comparators.)

Like · Reply · 5w

**Bob White** Hamish Laird Sounds like it is time for you to weigh in...

Like · Reply · 5w

Hamish Laird David Edwards Bob White lots of questions here. FPGAs are common in power control for custom peripherals. FPGAs are also falling in cost. We see the prices fall and continue to fall especially for the customers who have large accounts with vendors. There are also FPGAs in all silicon vendor companies which are used for power control chip prototyping.

Like · Reply · 5w

**Bob White** Hamish Laird OK, but what about combinations of FPGA and microcontroller cores? Don't you typically use a device with a significant FPGA married to an ARM core?

Like · Reply · 5w

Hamish Laird I do not know of the details for Intel or Lattice but Xilinx has made "If you want to buy it we will make it" statements for a long time.

Like · Reply · 5w

**Hamish Laird** Bob White We do use the FPGA with the ARM core attached as a development platform. We can then move to custom FPGA hardware to meet cost targets.

Like · Reply · 5w

**Hamish Laird** We do o control in the microcontroller or processor core as processors are just too slow.

$\text{Like} \cdot \text{Reply} \cdot 5w$

Hamish Laird That is - We do no control in the nmicrocontroller or processor core as processors are just too slow.

we had a lot of trouble finding a good digital engineer with FPGA and feedback control experience).

speed PWM feedback signal, filter it with audio bandwidth and feed it to a low cost external comparator the output of which goes back into the FPGA to complete the ADC feedback loop. That might be fun to design. Audio bandwidth should be good enough for controlling inverters, motor drives and the like.

Assume a 250MHz FPGA clock. With a 10 bit counter one could generate a 250kHz sawtooth. A simple three pole filter would filter the one bit PWM by just under 2,000x which would just sufficient for a 20kHz, 1024 step ADC bandwidth. I am just working this out as I type so I may be mistaken. The analog input would also need an anti-aliasing filter if the input contained high frequencies. Overall ADC bandwidth without too much phase shift might be only 5kHz or so. To bump up the bandwidth, one could have the FPGA produce two or three bits or do some oversampling tricks with in the FPGA.

Like · Reply · 5w · Edited

Seppo Turunen I am using the 3.3V variant of a Lattice Mach XO2 FPGA. The one with 2000 logic elements comes in a 100-lead TQFP package and has turned out to be more than sufficient for my project. For analog inputs I use LTC2315-12 5 Msps A/D converters that allow the FPGA to take plenty of samples from current and voltage waveforms for subsequent digital processing such as averaging, threshold detection and feedback control.

Like · Reply · 5w

Joel Holland Do you need a DSP as well? What switching frequency did you use and at what resolution? What do you think the maximum limits for those would be?

Like · Reply · 5w

Seppo Turunen Joel Holland I do not have a DSP. I am switching at 100 khz. The FPGA clock is 50 MHz. I am using registers of different length in the arithmetic, ranging from 12 to 32 bits. The longest ones are only needed as a scratchpad in divisions, though.

Like · Reply · 5w

Ray Ridley V Nice.

Like · Reply · 5w

Write a reply...

David Edwards Do any readers here have enough FPGA experience to comment on the last several remarks and/or answer the questions that did not get answered (read starting with the comment that begins, "I am not an FPGA expert . . . "

Like · Reply · 5w

Seppo Turunen There are families of small 3.3V FPGAs on the market with 256 to 50000 logic elements. The pin counts range from 32 and prices from 3-4 usd upwards.

Like · Reply · 5w

David Edwards Seppo Turunen Thanks for answering.

Like · Reply · 5w

Like · Reply · 5w

**Pranit Pawar I** created this thread because I looked for papers for optimal layout design and every paper just gives some 10-20 configurations and shows the resulting parasitics

of the arrangement. no reason, just graphs.

цке · керіу

Ray Ridley DExperience. And intelligent iteration. That's the fastest way to product.

Q

Like · Reply · 5w

Ray Ridley Graphs are good, that is how good engineering

The modern way is to want to solve it all with a computer, but that will never happen. Doesn't ever stop people trying though

Like · Reply · 5w

Daniel Ruiz We didn't use it to design or look for an optimized layout as much as to extract parasitic values to use in our simulations.

Like · Reply · 5w

David Edwards For most circuit traces and signals a few nH don't matter much. It's only those with high di/dt that may be problematic. In a switching supply what's always important is the inductance of the common source path between the gate drive and the main switched current of the MOSFET.

Like · Reply · 5w

Pranit Pawar Yes its a GaN high power drive, so di/dt and dv/dt is high

Like · Reply · 5w

Write a reply...

Darrell Hambley Pranit, You can get a good estimation of inductance if you break down your traces into linear elements. Use the equation for a strip-line over a plane:

Where: I is the length, d is the thickness of the board material and w is the width of the trace. All in cm. If you're working in inches, multiply by 2.54 cm/inch for:

L=32 nH-inch

For example, For w = 0.05 inch, d = 8 mils, l= 1 inch the trace inductance will be:

L = 32nH-inch \*1\*0.008/0.05=5.1nH.

You can verify this when you see a voltage spike on your o'scope from ground to the source of a MOSFET for example. If you know the rate of climb of current, di/dt, you will see that this spike voltage is close to:

V=L\*di/dt

Like · Reply · 5w

Ray Ridley of don't forget bond wire inductance. Plus, strip lines over planes probably don't exist in many places.

We should have a rule on the site, perhaps - metric units only!

Like · Reply · 5w

Pranit Pawar And for a plane, similar approach can be used to break down the polygon into small strips and integration has to be done?

Like · Reply · 5w

Darrell Hambley Many firms in aerospace use inches for board layout dimensions. I did leave the equation there in cm for those who only work in metric, assuming they don't know how to multiply by 2.54. Praint - yes, it can be integrated. Do pay attention to lead wires as Ray suggested. Always include source and drain lead inductance in your models.

kay kiuley v i believe that one of the coming strengths of Poli the digital control they are implementing, plus the motor drive aspects. I will let Albert Dunford speak more on that topic.

Like · Reply · 5w

Albert Dunford PSIM provides support for a great deal more than analog power supply. Not sure how NL5 fits into digital control, motor drives, embedded code gen, non-linear switch transitions, stability and convergence in larger simulations,

Like · Reply · 5w

David Edwards . Hello Ray Ridley,

I would love to see a similar comparison between your modification of LTspice, PSIM and SIMPLIS (and perhaps some others - see below). In addition to comparing plots, a listing of run times would be

This is taken from one my entries in the LTwiki:

The SPICE engine runs on fine tuned Modified Nodal Analysis technology, but competing technologies are emerging. Many simplify all nonlinear elements (diodes and other switches) into piecewise linear equivalents (2 or more line segments). This reduces the simulation to solving a repeating succession of related linear topologies. These are joined at their border points in time, but are perfectly linear in between. Each topology can be quickly solved without the many trial and error points of a nonlinear Newton-Raphson solution. Most notable of this breed are SIMPLIS (SiMetrix), PSIM (Powersim), PLECS (Plexim) and NL5 (Sidelinesoft).

These engines feature very quick steady state solvers for switched circuits and switched mode power supplies. Typically named POP or PSS (Periodic Operating Point or Periodic Steady State), a long, drawn out initial transient is avoided. Near instant POP/PSS and transient run speeds allows a time domain DFT ac analysis to be performed on switched circuits. Loopgain of switching power supplies and class-d amplifiers may be quickly analyzed in the time domain. Only a single nonlinear switched model is required - no need to resort to equivalent circuits with added "sampling effect" networks. Simulated results precisely match lab measurements (Venable, HP4194A, etc.) to and beyond the switching frequency.

Like · Reply · 5w · Edited

Ray Ridley Don't forget our simulation engine in RidleyWorks. Faster than any of them.

Like · Reply · 5w

Ray Ridley Sounds like a good job for someone who is (semi) retired.

Like · Reply · 5w

Ray Ridley Remember, all of these methods depend upon the circuit being stable. Otherwise there is no POP and you have to go back to small-signal models (which you should be using anyway.)

Like · Reply · 5w

Ray Ridley I believe the new-found speed of the PSIM has rendered it a moot point about whether the POP method is needed now. They have certainly cut deep into this prior advantage of Simplis.

LTspice is good too, you just have to wait. But what's the hurry? Layout a board while it does its thing.

So many options. What a great time to be a power designer!

Like · Reply · 5w

Yaqoob Muhammad User interface wise, I think, nothing can beat

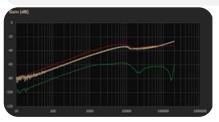

the scope makers for making this investment.

This doesn't alarm us at all - it is great to see such awareness of the need for Bode plots. What this is going to do is get people started on the topic, and get the measurements back into education.

Later, users will find that the performance can be quite erratic, depending on many factors, and what kind of thing your are trying to measure. Passive circuits - all is well. High performance noisy switchers, not so good.

We have been testing diligently for the last few months to see how things stack up versus the AP310, and we are very happy with the results. There are currently at least 8 different analyzers in our lab under review.

The good news for us is that nothing comes close to the AP310 analyzer for performance. You can see this in the plots below of power supply output impedance. The AP310 just cuts through the noise, and gives the same result regardless of circuit setup. Other wannabe analyzers are all over the place, especially in the range from 10 Hz to 100 Hz.

In these tests, the exact same circuit is being used, same cables, same isolator, everything.

If you need a rough idea, use whatever is at hand. But if you need reliable rugged performance under all conditions, the AP310 analyzer is the only one that gives it to you.

Comment

Like

Create

Ray Riciley 👽 Triis was a really illuminating and surprising set or experiments on 9 different analyzers. The AP310 reference is 20 dB below the others. This is a PSRR measurement.

Like · Reply · 5w

Ray Ridley More variability - see how much fun we have been

Like · Reply · 5w

Ray Ridley Here is one more plot of impedances, and a question. You can see the AP reference trace. Are the other measurements "good enough"?

Probably all depends on your industry, but I don't really know the answer to this.

Like · Reply · 5w

Ray Ridley To be honest, we can squeeze a loop gain out of almost anything. But it takes a lot of experience to do that. Most users won't have the expertise to do that, hence the AP310 with RidleyWorks that makes it a one-button setup.

PSRR and Output Impedance are much tougher to measure well. Many of the machines just can't do it.

Modern scopes certainly have processing power to handle it. They probably need to work on optimizing their analog circuitry for the task.

One thing to keep in mind when interpreting loop gain plots, some analyzers may be very good a presenting just the response to the fundamental test frequency, filtering out all harmonics and any other spurious signals. However, this may not yield the best indication of stability margin.

Why? Oscillation occurs at the frequency point which, if you were to magically break the loop at the input to the comparator (where the signals are analog), the signals on both sides of the loop would be identical. However, these may not be sine waves. If there are significant harmonics present, these must be taken into account in computing loop gain.

To be honest, I don't fully understand the math required, but this effect has been demonstrated in self-oscillating class d amplifiers where the oscillation point varies significantly from that predicted from the Bode analysis and enhanced .ac simulations. This problem is best illustrated by attempting to predict (using Bode analysis) the oscillation frequency of a simple Schmidt comparator oscillator circuit.

Like · Reply · 5w · Edited

Ray Ridley There is a conflict of optimizing the analog hardware to be a good scope versus being a good analyzer. Every scope we have measured so far, and some of the analyzers, have the same problem.

It makes them very susceptible to different test setups, which is not a good thing.

Like · Reply · 5w · Edited

Ray Ridley The AP 310 is not susceptible to these DUT setup changes. That is a very significant thing, this is a new realization for us, a result of all the testing we have been doing.

if you have our experience here, you can tell when things are not measuring right and maybe change setups. Without that, you are shooting in the dark, one of the reasons that people get frustrated with FRA measurements.

Like · Reply · 5w

David Edwards Frequency Response Analysis injects a smallish floating ac signal into the control loop, usually at a low impedance point. It then does a vector ratio analysis of signals measured from the two ends of the floating source with respect to ground. Discrete Fourier analysis techniques are used to reject noise.

Without thinking about it, one might assume there would be no need to adjust the size of the floating source over the measurement frequency range. However, at the low frequency end, due to extremely high loop gain, one of the vector signals gets very small and the floating source amplitude must be increased to avoid signal to noise issues. A similar effect happens at the high frequency end past unity loop gain.

I am correct to assume that the AP310 makes these adjustments automatically?

Like · Reply · 5w · Edited

for Type III compensation.

Like · Reply · 5w

Ray Ridley Isn't 2526 voltage mode?

Like · Reply · 5w

Col Johns it has a CS+ & CS- pin for terminating a cycle once 100mV is exceeded...

Like · Reply · 5w

Ray Ridley OK.

Write a comment...

(C) (C) (C)

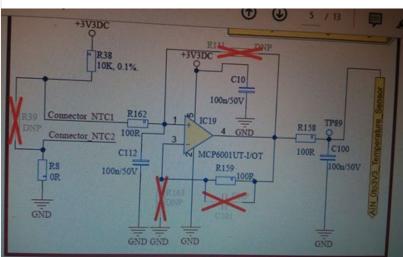

I am in trouble to measure the NTC temperature using microcontroller adc. I used STM32F405 controller . I did not use external reference in controller for ADC measurement. Internal reference is used. Now the internal reference varies from 1.18V to 1.24V which is approximate 2% of measurement error introduced. So if my temerature range is 0 to 35degC and hence maximum error is 0.7degC.

Q

I can not use external reference for MCU because STM32F405 is not having external reference pin in 64 pin package.

So can anybody suggest me any idea, solution or path to get rid of this

Supply voltage for NTC and Microcontroller is same dc rail and coming from LDO.

For now I am not considering the non linearity of NTC.

20 Comments

Ray Ridley Dlease try to do some cleaner graphic. It is so easy to use the snipping tool, then paste into the comment. People shouldn't have to get eyestrain reading what you post.

Like · Reply · 5w

Ray Ridley Why not add a precision reference if you need more accuracy?

Like · Reply · 5w

Shiv Kumar Mishra STM32F405 do not have external reference pin in 64pin pin package. That's the reason

Like · Reply · 5w

Bob White I think you need to do a full tolerance analysis on the entire sensor circuit. For example, you did not mention the tolerance of the temperature sensor. How does that compare to the error introduced by the variation in the internal reference voltage for the A2D converter?

Like · Reply · 5w

Yuval Iz Simply use an accurate voltage regulator and feed the microcontroller VDD and feed VDDA via a bead and a 0.1uf to gnd using this methode the ADC vref became the regulator voltage Analog device have accurate linear regulator you can use

Like · Reply · 5w

Charlie Elliott Feed a vref into another ADC input and do the compensation in software!

Like · Reply · 5w

Charlie Elliott Shiv Kumar Mishra - I and other members of this group are very happy to help but we are typically not prepeared to do the actual job without being paid for it!! Please think carefully about what I have suggested and I am sure what you need to do will become clear.

Like · Reply · 5w

Ray Ridley Let me guess....."can't afford a Vref in this design?"

Like · Reply · 5w

Shiv Kumar Mishra Sometimes we made worng guess. MCU does not have external reference pin 64pin of stm32f405

Like · Reply · 5w

Julio La Leggenda Use a current source to generate a precise voltage reference.

Like · Reply · 5w · Edited

Broox Le What exactly is the problem? - is the error tolerance not tight enough for your application?

Like · Reply · 5w · Edited

Alex Berestov 1. Did not you know If a ruler is 0.7% accurate that's all you gonna get?

2. Did not you read datasheet before you designed thingy of yours?

3. It's a good lesson, next time think before you do.

Introduce good ref into design of yours and measure it with free adc

P.S. It's power supply (not analog or micro) design group BTW.

Like · Reply · 5w · Edited

Syed Rafi Sifath Palal 1. Have a precise regulator is a good option, 2. also possible to calibrate using software, eg use another adc pin and measure a fixed voltage then calculate the variation from your base device then include this variation in you temperature calculation. The varietion input you can take in uart and store in flash 3. You can use a potentiometer in series with ntc and can adjust the output manually for different devices. The resistance of pot might change with temperature though, but I guess this still reduce your error

4. Software calibration using only ntc also possible, you measure your base ntc reading, and target ntc reading, add the variation calculation in Target ntc using uart and store it in a non volatile memory.

Like · Reply · 5w

Frank Warnes I always prefer the LM50 to using an NTC. Gets rid of all the complication

Like · Reply · 5w

Yuri de Klerk Or MP9700

Like · Reply · 5w

Charlie Elliott "Yuri de Klerk AKA "the thermistor buster"

Like · Reply · 5w

Milovan Kovacevic Sometimes you earn more money, sometimes you make your life easier, sometimes both, sometimes neither

Like · Reply · 5w

Write a reply..

Dave Lanerty You can't estimate cost until you have a product spec and an idea of what type of design is required to meet that spec.

Like · Reply · 5w

Bob White And aside from the very important specifications, what is the production volume? The cost difference between making 100 per year and 100,000 per year is orders of magnitude (see Hamish's note that high volume telco rectifiers sell for US\$0.03 per watt).

Like · Reply · 5w

Jeremy Lister The sales manager will define the price and you make the design fit that price...a route to disaster

Like · Reply · 5w

Ray Ridley Ocorollary to this:

The system definer will define the enclosure, and you make the design fit that space.

Like · Reply · 5w

Ray Ridley Disaster recovery is our thing. By the time people come to us for a design, they need it now, and cost is not the first thing on the list any more. The disaster has already happened, and there is no power supply available for the product because things were designed with only price in mind.

We do FAST prototypes for people in trouble. It's stressful sometimes, but rewarding. Our last fast prototype was 100 W isolated converter design, build and test in 1 week. That included all magnetics designed and wound as part of the process.

Before that was a 400 W flyback converter, also completed in 1 week

It is not \$0.03 per watt 🙂

Like · Reply · 5w · Edited